Product Summary

The XCR3512XL-10PQ208I is a 3.3V, 512 macrocell CPLD targeted at power sensitive designs that require leading edge programmable logic solutions. A total of 32 function blocks of the XCR3512XL-10PQ208I provide 12,800 usable gates. Pin-to-pin propagation delays are 7.5 ns with a maximum system frequency of 127 MHz.

Parametrics

XCR3512XL-10PQ208I features: (1)Lowest power 512 macrocell CPLD; (2)7.5 ns pin-to-pin logic delays; (3)System frequencies up to 127 MHz; (4)512 macrocells with 12,800 usable gates; (5)Available in small footprint packages; (6)Optimized for 3.3V systems; (7)Advanced system features; (8)Fast ISP programming times; (9)Port Enable pin for additional I/O; (10)2.7V to 3.6V supply voltage at industrial grade voltage range; (11)Programmable slew rate control per output; (12)Security bit prevents unauthorized access; (13)Refer to XPLA3 family data sheet (DS012) for architecture description.

Features

XCR3512XL-10PQ208I specifications: (1)VOH Output High voltage: 2.4 V; (2)VOL Output Low voltage: 0.4 V; (3)IIL Input leakage current: –10 to 10 μA; (4)IIH I/O High-Z leakage current: –10 to 10 μA; (5)ICCSB Standby current: 100 μA; (6)ICC Dynamic current: TBD mA; (7)CIN Input pin capacitance: 8 pF; (8)CCLK Clock input capacitance: 12 pF; (9)CI/O I/O pin capacitance: 10 pF.

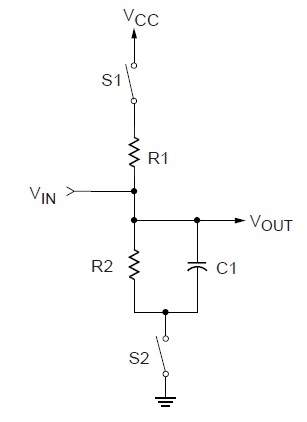

Diagrams

|

XCR3032 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

XCR3032A: 32 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

XCR3032C |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

XCR3032XL |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

XCR3032XL 32 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

XCR3032XL-10CS48I |

|

IC CPLD 3.3V ZERO PWR 48-CSP |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))