Product Summary

The SN74GTLPH1612DGG is a 18-bit lvttl-to-gtlp adjustable-edge-rate universal bus transceiver. It provides LVTTL-to-GTLP and GTLP-to-LVTTL signal-level translation. The SN74GTLPH1612DGG allows for transparent, latched, clocked, or clock-enabled modes of data transfer. The SN74GTLPH1612DGG provides a high-speed interface between cards operating at LVTTL logic levels and a backplane operating at GTLP signal levels. High-speed (about three times faster than standard TTL or LVTTL) backplane operation is a direct result of GTLP’s reduced output swing (<1 V), reduced input threshold levels, improved differential input, OEC circuitry, and TI-OPC circuitry. Improved GTLP OEC and TI-OPC circuits of the SN74GTLPH1612DGG minimize bus-settling time and have been designed and tested using several backplane models.

Parametrics

SN74GTLPH1612DGG absolute maximum ratings: (1)VCC BIAS VCC Supply voltage range: –0.5 to 4.6 V; (2)VI Input voltage range: -0.5 to 7 V; (3)VO Voltage range applied to any output in the high-impedance or power-off state: –0.5 to 7 V; (4)IO Current into any A-port output in the high state: 48 mA; (5)Continuous current through each VCC or GND: ±100 mA; (6)IIK Input clamp current: –50 mA; (7)IOK Output clamp current: –50 mA; (8)Tstg Storage temperature range: –65 to 150 ℃.

Features

SN74GTLPH1612DGG features: (1)Member of the Texas Instruments Widebus Family; (2)UBT Transceiver Combines D-Type Latches and D-Type Flip-Flops for Operation in Transparent, Latched, Clocked, or Clock-Enabled Modes; (3)TI-OPC Circuitry Limits Ringing on Unevenly Loaded Backplanes; (4)OEC Circuitry Improves Signal Integrity and Reduces Electromagnetic Interference; (5)Bidirectional Interface Between GTLP Signal Levels and LVTTL Logic Levels; (6)LVTTL Interfaces Are 5-V Tolerant; (7)High-Drive GTLP Outputs (100 mA); (8)LVTTL Outputs (–24 mA/24 mA); (9)Variable Edge-Rate Control (ERC) Input Selects GTLP Rise and Fall Times for Optimal Data-Transfer Rate and Signal Integrity in Distributed Loads; (10)Ioff, Power-Up 3-State, and BIAS VCC Support Live Insertion.

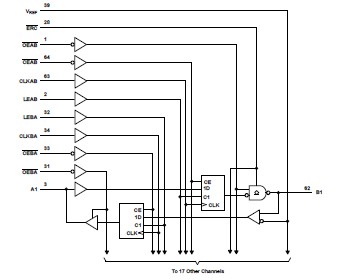

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

SN74GTLPH1612DGGR |

Texas Instruments |

Translation - Voltage Levels Quadruple Bilateral Analog Switch |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

SN7400 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

SN7400D |

Texas Instruments |

Gates (AND / NAND / OR / NOR) Quad 2-input Positive-NAND gates |

Data Sheet |

|

|

||||||||||||

|

SN7400DE4 |

Texas Instruments |

Gates (AND / NAND / OR / NOR) Quad 2-input Positive-NAND gates |

Data Sheet |

|

|

||||||||||||

|

SN7400DG4 |

Texas Instruments |

Gates (AND / NAND / OR / NOR) Quad 2-input Pos- NAND |

Data Sheet |

|

|

||||||||||||

|

SN7400DR |

|

IC QUAD 2IN POS-NAND GATE 14SOIC |

Data Sheet |

Negotiable |

|

||||||||||||

|

SN7400DRE4 |

|

IC QUAD 2IN POS-NAND GATE 14SOIC |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))