Product Summary

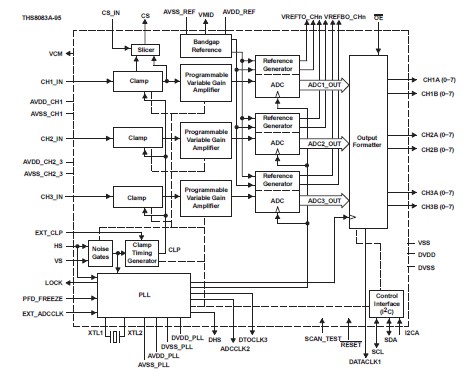

The THS8083APZP is a 3.3V video and graphics digitizer with digital PPL. The device supports pixel rates up to 80 MHz. Therefore, the THS8083APZP can be used for PC graphics digitizing up to the VESA standard of XGA (1024 × 768) resolution at 75 Hz screen refresh rate, and in video environments for the digitizing of digital TV formats, including HDTV. The THS8083APZP is powered from a single 3.3-V supply and integrates a triple high-performance A/D converter with clamping functions and variable gain, independently programmable for each channel. The applications of the THS8083APZP include: LCD desktop monitors and LCD or DMD-based projection systems, Videoconferencing, PCTV set-top boxes, digital TV sets, and multimedia cards, Scan rate/image resolution converters, Video/graphics digitizing equipment (RGB or YUV-based).

Parametrics

THS8083APZP absolute maxing ratings: (1)Supply voltage range: Analog supplies to AGND, Digital supplies to DGND: -0.5 to 4.5 V, Analog supplies to digital supplies, AGND to DGND: -0.5 to 0.5 V; (2)Digital input voltage range to DGND, VI: -0.5 to DVDD + 0.5 V; (3)Analog input voltage range to AGND, VI: -0.5 to AVDD + 0.5 V; (4)Bandgap reference to AGND: -0.5 to AVDD + 0.5 V; (5)Reference voltage (VREFTO_CHx,VREFBO_CHx) input range to AGND, Vref: -0.5 to AVDD + 0.5 V; (6)Operating free-air temperature range, TA: 0℃ to 70℃; (7)Storage temperature range, Tstg: -55℃ to 150℃.

Features

THS8083APZP features: (1)Clamp: 256-step programmable RGB or YUV clamping during external or internal clamp timing window; (2)PGA: 6-bit coarse/5-bit fine programmable gain amplifier; (3)ADC: 8 bit 80 MSPS A/D converter; (4)Composite sync: Integrated sync-on-green/sync-on-luminance extraction from green/luminance channel or from dedicated input; (5)Support for dc and ac-coupled input signals; (6)Fully integrated digital PLL (including loop filter) for pixel clock generation; (7)13-80 MHz pixel clock generation from reference input; (8)Adjustable PLL loop bandwidth for minimum jitter or fast acquisition/wide capture range modes; (9)5-bit programmable subpixel accurate positioning of sampling phase; (10)Noise gates on HS and VS inputs to avoid false PLL updating.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

THS8083APZP |

Texas Instruments |

Video A/D Converter ICs Triple 8B 80 MSPS 3.3V YUV/RGB |

Data Sheet |

Negotiable |

|

||||

|

THS8083APZPG4 |

Texas Instruments |

Video A/D Converter ICs Tr 8B 95MSPS 3.3V Vid & Graphics Dig |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))